## International Journal of Advance Research in Science and Engineering Vol. No.5, Special Issue No. 01, March 2016 www.ijarse.com

# DESIGN OF 8 PORT ROUTER FOR NOC USING VERILOG

Rekha S<sup>1</sup>, Dr. A. M Bhavikatti<sup>2</sup>

<sup>1</sup>Research Scholar Vtu Belgaum, Karnataka, (India) <sup>2</sup>Dept.of Computer Science Engineering Bkit, Bhalki, Karnataka, (India)

### ABSTRACT

Multiprocessor system on chip is emerging as a new trend for System on chip design but the wire and power design constraints are forcing adoption of new design methodologies. Researchers pursued a scalable solution to this problem i.e. Network on Chip (NOC). Network on chip architecture better supports the integration of SOC consists of on chip packet switched network. The proposed design of 8 port router is simulated and synthesized in Xilinx ISE 9.2i and the source code is written in Verilog.

### Keywords: Network on Chip, 8 port router, Xilinx ISE 9.2i.

### I. INTRODUCTION

as per Moore's law the density of chip doubles every 18 months, so the parameters of a single chip get affected due to increase of processing elements on a chip. NOC is a packet switched on-chip data transfer network that solves challenges faced by SOC of bus based communication. The basic ingredients of NOC are topology which defines the communication architecture, routing technique which decides how the data is routed from sender to receiver, routers and switching technique which determines when the data flow through the routers.

NOC used only point to point wires for all network sizes and it increases the utilization of wires. The focus of paper is design of Network on chip five port routers. The effective on chip communication is achieved by router's routing functionality and efficient arbitration [1]. The main goal of this paper is the design of power and area efficient on chip router.

### **II. OVERVIEW**

A variety of interconnection schemes are currently in use, including crossbar, buses and NOCs. Of these, later two are dominant in research community. However buses suffers from poor scalability because as the number of processing elements increases, performance degrades dramatically. Hence they are not considered where processing elements are more. To overcome this limitation attention has shifted to packet-based on-chip communication networks, known as Network-On-Chip (NOC).

### **III.ROUTER**

System on chip is a complex interconnection of various functional elements. It creates communication bottleneck in the gigabit communication due to its bus based architecture. Thus there was need of system that

## International Journal of Advance Research in Science and Engineering Vol. No.5, Special Issue No. 01, March 2016 www.ijarse.com

explicit modularity and parallelism, network on chip possess many such attractive properties and solve the problem of communication bottleneck. It basically works on the idea of interconnection of cores using on chip network. The communication on network on chip is carried out by means of router, so for implementing better NOC, the router should be efficiently design.

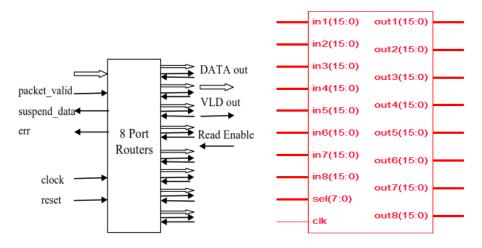

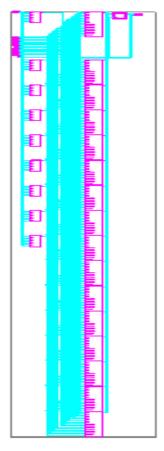

Figure-1: Block diagram of 8 port router Figure-2: Synthesized 8 port block diagram in Xilinx ISE

**Figure-3: Schematic of 8 Port router**

## International Journal of Advance Research in Science and Engineering 🔬

Vol. No.5, Special Issue No. 01, March 2016

www.ijarse.com

IJARSE ISSN 2319 - 8354

### IV. RESULT ANALYSIS

**Design Statistics**

| # IOs               | : 265 |

|---------------------|-------|

| Cell Usage :        |       |

| # BELS              | : 125 |

| # GND               | :1    |

| # LUT2              | : 18  |

| # LUT3              | :4    |

| # LUT4              | : 96  |

| # MUXF5             | : 5   |

| # VCC               | : 1   |

| # FlipFlops/Latches | : 16  |

| # FDS               | : 16  |

| # Clock Buffers     | :1    |

| # BUFGP             | : 1   |

| # IO Buffers        | : 264 |

| # IBUF              | : 136 |

| # OBUF              | : 128 |

|                     |       |

### **Device utilization summary:**

Selected Device : 3s50pq208-5

| Number of Slices:           | 69  | out of | 768  | 8%   |

|-----------------------------|-----|--------|------|------|

| Number of Slice Flip Flops: | 16  | out of | 1536 | 1%   |

| Number of 4 input LUTs:     | 118 | out of | 1536 | 7%   |

| Number of IOs:              | 265 |        |      |      |

| Number of bonded IOBs:      | 265 | out of | 124  | 213% |

| Number of GCLKs:            | 1   | out of | 8    | 12%  |

### **Timing Summary:**

Minimum period: 2.259ns

Minimum input arrival time before clock: 9.966ns Maximum output required time after clock: 6.490ns

Maximum combinational path delay: No path found

### International Journal of Advance Research in Science and Engineering

Vol. No.5, Special Issue No. 01, March 2016 www.ijarse.com

IJARSE ISSN 2319 - 8354

### **V. SIMULATION RESULTS**

| Current Simulation<br>Time: 1000 ns |          | 713.8           |          |         |          |     |     |  |

|-------------------------------------|----------|-----------------|----------|---------|----------|-----|-----|--|

|                                     |          | 20              | )        | 400     | 600      | 800 | 100 |  |

| 🗄 🕅 out1[15:0]                      | 16'h0002 |                 | 16'hXXXX |         | 6'h0002  |     |     |  |

| 🗄 🕅 out2[15:0]                      | 16'h0002 |                 | 16'hXXXX |         | 6°h0002  |     |     |  |

| 🖬 😽 out3[15:0]                      | 16'h0002 |                 | 16'hXXXX |         | 6'h0002  |     |     |  |

| 🗉 🚮 out4[15:0]                      | 16'h0002 | 16'hXXXX        |          |         | 6'h0002  |     |     |  |

| 🗉 🚮 out5[15:0]                      | 16'h0002 | 16°hXXXX        |          |         | 6'h0002  |     |     |  |

| 🗉 🚮 out6[15:0]                      | 16'h0002 | 16°hX000X       |          |         | 6'h0002  |     |     |  |

| 🗉 🚮 out7[15:0]                      | 16'h0002 | 16'hXXXX        |          | 6'h0002 |          |     |     |  |

| 🗉 🚮 out8[15:0]                      | 16'h0002 | 16'hXXXX        |          |         | 6'h0002  |     |     |  |

| 🗉 🚮 sel[7:0]                        | 8'h02    | 8'h00 X 8'h06 X |          |         | 8'h02    |     |     |  |

| oll dk                              | 1        |                 |          |         |          |     |     |  |

| 🖬 😽 in1[15:0]                       | 16'h0001 | 16'h0000        | 16'h0002 | X       | 16'h0\01 |     |     |  |

| 🗉 🚮 in2[15:0]                       | 16'h0002 | 16'h0000        | 16'h0003 | X       | 16'h002  |     |     |  |

| 🗉 🚮 in3(15:0)                       | 16'h0003 | 16'h0000        | 16'h0005 | X       | 16'h0103 |     |     |  |

| 🗉 🚮 in4(15:0)                       | 16'h0004 | 16'h0000        | 16'h0006 | X       | 16'h0\04 |     |     |  |

| 🗉 🚮 in5(15:0)                       | 16'h0005 | 16'h0000        | 16'h000A | X       | 16'h0005 |     |     |  |

| 🗉 🚮 in6(15:0)                       | 16'h0006 | 16'h0000        | 16'h000B | X       | 16'h0106 |     |     |  |

| 🗉 😽 in7(15:0)                       | 16'h0007 | 16'h0000        | 16'h0002 | X       | 16'h0107 |     |     |  |

| 🗉 🚮 in8(15:0)                       | 16'h0008 | 16'h0000        | 16'h0004 | X       | 16'h0008 |     |     |  |

### VI. CONCLUSION

The proposed design of 8 port router is simulated and synthesized in Xilinx ISE 9.2i and the source code is written in Verilog. This proposed design has high speed and less delay. The Total delay is 2.259ns.

### REFERENCES

- [1] P.B.Domkondwar and Dr. D.S.Chaudhari, "Implementation of Five Port Router Architecture Using VHDL" IJARCSEE Volume 1,Issue 3, May 2012.

- [2] P. Kaveri, G.R.K.Prasad, FazalNoorbasha"Router design using cadence encounter" IJRTE, May 2013.

- [3] BhavanP.Shrivastava, KavitaKhare"Design of improved routers for network on chip" IJCTT, sep 2013.

- [4] B. Attia, W. Chouchene, A. Zitouni, N. Abid, and R. Tourki, "A Modular Router Architecture Desgin For Network on Chip" 8<sup>th</sup>International Multi-Conference on Systems, Signals & Devices 2011.

- [5] M. Sood and V. Tiwari "Performance Evalution of Noc Router Architecture by Using VHDL" Vol-II No. 2 pages 154-158, Oct-2010Jan-2011.