International Journal of Advance Research in Science and Engineering Volume No.06, Issue No. 10, October 2017 www.ijarse.com IJARSE

# Design and Analysis of 4bit Array Multiplier using 45nm Technology:

A.Karthikeyan<sup>1</sup>, V.Narayanan<sup>2</sup>, M.Ram Kumar<sup>3</sup>, S.Praveen<sup>4</sup>

<sup>1</sup>Assistant Professor/ECE, SNS College of Technology, Coimbatore, (India) <sup>2,3,4</sup>UG-Scholar/ECE, SNS College of Technology, Coimbatore, (India)

#### ABSTRACT

In digital signal processors multipliers play a major role because, high multiplication process is carried out in hardware part in digital circuits. Array multiplier also requires less space for implementation in ICs and is an efficient way of multiplication in digital integrated circuits [3-4]. In this paper we have designed and analysed a four bit array multiplier using 45nm CMOS process. Array multiplier consumes less power and is highly efficient in terms of speed. In this work a 4-bit array multiplier and its functionality is verified using Xilinx ISE Tool. In order to analyse the speed and power a 4-bit array multiplier is simulated using SPICE Tools with a supply voltage of 1volt the room temperature simulation results indicates the 4-bit multiplier consumes a power of 160µw and has a delay of 185pS for 45m CMOS process.

Keywords— array multiplier, , digital processor, full adders power and delay &45nm technology

#### I. INTRODUCTION

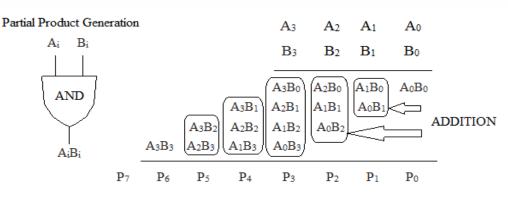

The demand for portable and embedded digital signal processing systems (DSP) has been increasing as a result of the speed growth of semiconductor technology and also due to the expanding of computers, televisions, computer aided gadgets and signal processing applications. Increasing the speed and reducing the power consumption are most essential requirements for present and next generation processors. The customization and optimization at all levels of the design is essential for the minimum usage of power consumption for all the digital integrated circuits and systems. The main optimization includes the semiconductor and its processing technology which is used to implement in the digital circuits, the circuit style and its topology and the architecture for implementing the circuits [6-9]. Digital multipliers are the commonly used circuits in applications such as digital signal processing for convolution, Fast Fourier Transform (FFT), digital filters and microprocessors in its arithmetic and logic unit. Increasing the speed is more essential since multiplication process dominates the execution time of most digital signal processing applications. In many digital signal processing applications, the multiplier lies in the critical delay path and ultimately determines the performance of the processor. The speed, delay and power consumption of Multipliers are more important in digital signal processors as well as in general processors since it dominates the chip power consumption and operation speed. There are architectures that are proposed in literature to perform multiplication, each offering different advantages and having trade off in terms of speed, power consumption, and area and circuit complexity. Let A0, A1, A2, A3 and B0, B1, B2, B3 be the two four bit binary numbers to be

#### International Journal of Advance Research in Science and Engineering Volume No.06, Issue No. 10, October 2017 www.ijarse.com IJARSE

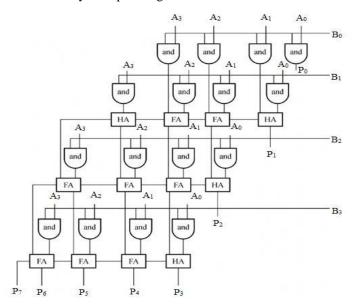

The above figure represents the conventional multiplication done at proper manner in above, the conventional array multiplier in multiplied in 4x4 multiplier and the outputs are P0, P1, P2, P3, P4, P5, P6 and P7.

#### **II. ARCHITECTURE OF MULTIPLIER**

The computation speed of blocks in digital signal processors (DSP) have increased dramatically over the past four decades resulting from the rapid advancement of various technologies. The execution speed of multipliers depends on two factors, one is the semiconductor technology used and the other is the multiplier architecture [5]. Multiplication process involves a more series of repeated additions. Therefore adders are the basic building blocks of digital multipliers. Increasing the speed of the adder, results in an increase in the speed of the multipliers. The area of the multipliers can be minimized by reducing the number of transistors required for implementing full adder circuits. Array multiplier has a unique and little modified process compared to conventional multiplication process .The proposed 4 bit array multiplier are discussed below,

#### **III.PROPOSED 4-BIT ARRAY MULTIPLIER**

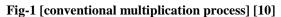

The structure of 4 x 4 Bit Array Multiplier is shown in fig.2.and fig.3. The working array multiplier is based on the principle of shift and algorithm. In this Multiplier, the partial products can be generated using AND gates and the summation of partial products can be performed using Full Adders and Half Adders. In an n x n array multiplier, n x n and gates computes the partial products and the addition of partial products can be performed by using n x (n-2) full adders and n half adders[10]. The bit array multiplier is easy to design and it uses a pipelined architecture. Since the worst case delay of the bit array multiplier is proportional to the width of the multiplier, the speed performance will be degraded for wide fan-in multipliers

#### International Journal of Advance Research in Science and Engineering Volume No.06, Issue No. 10, October 2017 www.ijarse.com ISSN: 2319-8354

# A. SCHEMATIC DIAGRAM OF ARRAY MULTIPLIER:

The Schematic diagram of 4 bit array multiplier is given below with a full schematic below:

Fig.3 Schematic Diagram Representation [10]

#### **B**• SIMULATION RESULTS:

The simulations have been proven for 4-bit array multiplier through Xilinx ISE Tool and results are displayed below:

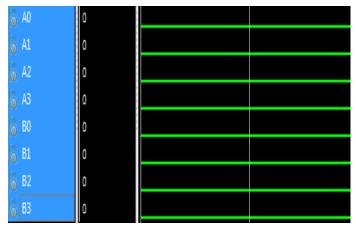

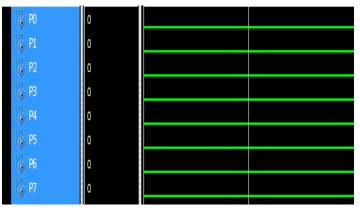

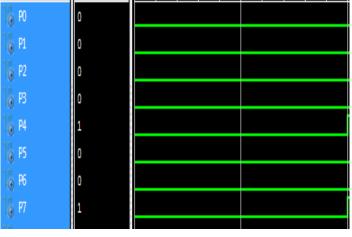

Case1: In this case we have given inputs and outputs as;

Input: A0=0; A1=0; A2=0; A3=0; B0=0; B1=0; B2=0; B3=0.

**Fig.4 Input simulation Result**

Output: P0=0; P1=0; P1=0; P2=0; P3=0; P4=0; P5=0; P6=0; P7=0:

### International Journal of Advance Research in Science and Engineering 🔔 Volume No.06, Issue No. 10, October 2017 www.ijarse.com

Fig.5 Output Simulation Result

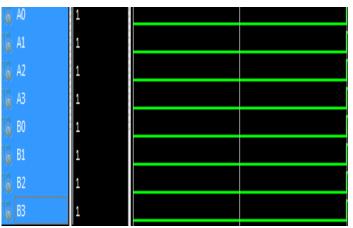

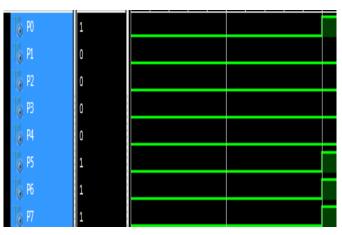

Case2: In this case we have given inputs and outputs as;

Input: A0=1; A1=1; A2=1; A3=1; B0=1; B1=1; B2=1; B3=1.

#### **Fig.6 Input Simulation Result**

Output: P0=1; P1=0; P1=0; P2=0; P3=0; P4=0; P5=1; P6=1; P7=1.

**Fig.7 Input Simulation Result**

Case3: In this case we have given inputs and outputs as;

## International Journal of Advance Research in Science and Engineering 🔔 Volume No.06, Issue No. 10, October 2017 www.ijarse.com

IJARSE ISSN: 2319-8354

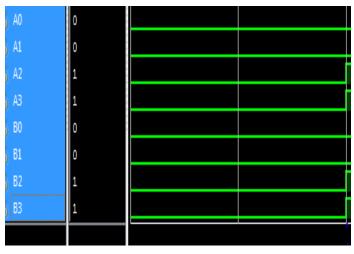

Input: A0=0; A1=0; A2=1; A3=1; B0=0; B1=0; B2=1; B3=1.

**Fig.8 Input Simulation Result**

Output: P0=1; P1=0; P1=0; P2=0; P3=0; P4=0; P5=1; P6=1; P7=1.

**Fig.9 Output Simulation Result**

The Power and Delay characteristics are observed using SPICE Tool and the Results are verified they are displayed in TABLE-1:

| Multiplier       | Delay(pS) | Power(µw) |

|------------------|-----------|-----------|

| Array Multiplier | 185pS     | 160µw     |

#### **IV. CONCLUSION:**

Thus, In this paper we have designed and analyzed the 4-bit Array Multiplier using 45nm CMOS process its functionality were verified using Xilinx ISE Tool and its Power and Delay characteristics were calculated using SPICE Tools under 45nm CMOS process.

### International Journal of Advance Research in Science and Engineering Volume No.06, Issue No. 10, October 2017 www.ijarse.com

**V.REFERENCES:**

- D. Kudithipudi, Eugene John, "Implementation of Low Power Digital Multipliers Using 10 Transistor Adder Blocks", Journal of Low Power Electronics, vol.1, pp.1-11, 2005.

- [2] I.S.Ab u-Khater, A.Bellaouar, and M.I.Elmasry, Circuit techniques for CMOS low power highperformance multipliers. IEEE Journal of Solid State Circuits, Vol31, pp.1535–1546.1996.

- G.-K.Ma and F.J.T aylor, Multiplier policies for digital signal processing. IEEE ASSP Magazine (1990), pp.6–19.

- [4] T.K.Calla way and E.E.Swartzlander, Jr., Power delay characteristics of CMOS multipliers.

Proceedings of the 13th International Symposium on Computer Arithmetic (1997), pp.26–32.

- [5] Y. C. Lim, "Single-precision multiplier with reduced circuit complexity for signal processing applications," IEEE Trans. Comput., vol. 41, no. 10, pp. 1333–1336, Oct. 1992.

- [6] A.Karthikeyan, N.Rajeshwaran," design and implementation of multiple fault diagnosis on vlsi circuits using artificial neural networks", International Journal of Advances in Engineering & Technology, May 2012. PP685-695.

- [7] SumitaVaidya and Deepak Dandekar, "Delay-Power Performance comparison of Multipliers in VLSI Circuit Design", International Journal of Computer Networks & Communications (IJCNC), Vol.2, No.4, pp. 47 -56, July 2010.

- [8] J. M. Rabaey, A. Chandrakasan. and B. Nikolic. (Eds. ), Digital Integrated Circuits, Prentice Hall Publications (2003)

- [9] Predictive Technology Model (PTM). 22 nm High Performance Technology of PTM Model.[Online].Available:http://www.eas.asu.edu

- [10] S.Sabeetha, J.Ajayan, S.Shriram, K.Vivek, V.Rajesh(dept of ECE MIT Pondicherry)"a study of performance comparison of digital multiplier using 22nm strained silicon technology".(ICECS-2015).

- [11] Reza FaghihMirzaee,MohammedHosseinMoaiyeri,KeivanNavi(2010), "High Speed NP-CMOS and Multi Output Dynamic Full Adder Cells".

- [12] B.Sathiyabama, Dr.S.Malarkka (2012), " Low power novel hybrid adders for datapath circuits in DSP processor", Indian Journal of Computer Science and Engineering (IJCSE), Vol.3No.1, ISSN 0976-5166.

- [13] YingtaoJiang, Abdulkarim Al Sheraidah, Yuke Wang, Edwin Sha. And Jin Gyun Chung (2004), "A novel multiplexer based low power full adder", IEEE Transactions on circuits and systems -2, Vol.51, No.7, pp1057-7130.

- [14] N.Ravi, Dr.T.JayachandraPrasad ,Dr.T.SubbaRao,Y.Subbaiah (2011), "A Novel Low Power, Low Area Array Multiplier Design for DSP Applications", Proceedings of 2011 International Conference on Signal Processing, Communication, Computing and Networking Technologies (ICSCCN 2011).

- [15] TriptiSharma, Prof.B.P.Singh, K.G.Sharma, NehaArora "High speed , low power 8t full adder cell with 45% improvement in threshold loass problem".

- [16] ShivshankarMishra, V, Narendar, Dr.R.A.Mishra (2011), "On the design of high performance CMOS 1 bit full adder circuits", Proceedings published by International Journal of Computer Applications (ICVCI2011).

#### International Journal of Advance Research in Science and Engineering Volume No.06, Issue No. 10, October 2017 www.ijarse.com IJARSE

- [17] M.B. Damle, Dr. S. S. Limaye (2012), "Low- power Full Adder array-based Multiplier with Domino Logic", International Journal of advanced Research in Computer Engineering & Technology, Vol.1, Issue 4, June 2012, ISSN:2278-1323

- [18] A.Karthikeyan, V.Pradeep, G.Praveen Kumar, S.Lakshmanan (2015) "An efficient vlsi implementation for 64 bit error tolertant adders", in International Journal of Advance Research In Science And Engineering IJARSE, Vol. No.4, Special Issue (02), February 2015 PP 596-603.

- [19] S. S. Kidambi, F. El-Guibaly, and A. Antoniou, "Area-efficient multipliers for digital signal processing applications," IEEE Trans.Circuits Syst II, Exp.Briefs, vol. 43, no. 2, pp. 90–95, Feb.1996.

#### **AUTHORS PROFILE:**

**KARTHIKEYAN.A**received his B.Tech., degree specialized in Electronics and Communication Engineering in Bharathiyar College of Technology, Karaikal in the year 2008 under Pondicherry University, Pondicherry, and M.E., degree in VLSI Design in SNS College of Technology, Coimbatore in the year 2012 under Anna University, Chennai. He is now

working as Assistant Professor in the Department of Electronics and Communication Engineering, SNS College of Technology, Coimbatore, Tamilnadu, India. Currently he is pursuing Ph.D. in Anna University, Chennai. His area of interest includes Wireless Sensor Networks, VLSI Design Techniques and Computer networking. He is a Life Member of the International Society for Research and Development (MISRD), International Association of Engineers (MIAENG) and International Association of Computer Science and Information Technology (MIACSIT).

**NARAYANAN** .Vwas born on 9th may 1998 .He is currently pursuing his BE-degree at SNS College of technology. He had already published two Journals on VLSI based architecture in International journal and Conference. His area of interest is DSP applications and VLSI-Design. He also done some mini-projects in intercollege level project expo.

**RAM KUMAR.M** was born on 12th october1997. He is currently pursuing his BE-Degree at SNS College of technology. He is more interested on Nano Electronics. His area of interest is DSP applications and VLSI-Design. He is more interested on python language and he have basic idea on raspberry-pi controller.

**PRAVEEN.S** was born on 26th may 1997.He is currently pursuing his BE-Degree in SNS college of technology. He is more interested on upcoming semiconducting technologies. His area of interest is on Low power VLSI and VLSI-Design he did some mini projects based on automatic controls in project expo.